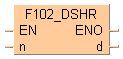

F102_DSHR

F102_DSHRInstruction redondante

Instruction redondante remplacée par : SHR

Cette instruction décale la valeur de la sortie d vers la droite. Le nombre de bits de la sortie d à décaler vers la droite est spécifié par la valeur affectée à l’entrée n. Ce décalage peut être compris entre 0 et 255 (uniquement l’octet de poids faible de n est effectif). Les bits effacés à cause du décalage sont mis à 0. Lorsque l’entrée n = 0, aucun décalage n’est exécuté. Une distance de décalage supérieure à 32 n’a pas de sens car lorsque n = 32, la valeur de la sortie d est déjà complétée avec des zéros. Le bit en position n - 1 (le dernier bit décalé à droite) est simultanément sauvegardé dans la variable système sys_bIsCarry (drapeau de retenue) et peut être évalué en conséquence. Lorsque n = 0, le contenu du drapeau de retenue ne change pas

Entrée

Nombre de bits à décaler (intervalle : 16#0 à 16#FF)

Sortie

Zone de 32 bits à décaler vers la droite

Si le bit en position n-1 a la valeur 1.