Beim Abarbeiten von Netzwerken im KOP- oder FBS-Editor gilt die folgende Reihenfolge:

Der Compiler beginnt links oben an der Stromschiene. Wenn Elemente direkt an die Stromschiene angeschlossen sind, wird der Strom durch alle diese Elemente geleitet. Wenn es keine direkt angeschlossenen Elemente gibt, beginnt der Compiler mit allen Eingängen. Eingänge werden von Control FPWIN Pro7 so behandelt, als wären Sie zur Abarbeitung bereit.

Anschließend sucht der Compiler nach dem Element auf der höchsten Ebene. Wenn sich zwei Elemente auf der gleichen Ebene (Linie) befinden, arbeitet er zuerst das linke Element ab. Wenn es sich bei dem Element um einen Ausgang oder den Aufruf einer Funktion bzw. eines Funktionsbausteins handelt, erzeugt der Compiler den entsprechenden Code. Hierbei können temporäre Variablen eingefügt werden, um das Signal zwischenzuspeichern bzw. im Stapelspeicher (Stack) abzulegen.

Der Compiler leitet den Ausgangsstrom des Elements, das im 2. Schritt abgearbeitet wurde (Zwischenergebnis), an alle direkt angeschlossenen Elemente. Dann wertet er das nächste Element aus. Anschließend beginnt er wieder bei Schritt 2, bis alle Elemente ausgewertet oder kein Element mehr zur Auswertung verfügbar ist.

Die Abarbeitung wird unterbrochen bzw. beendet.

Im Folgenden finden Sie einige Beispiele für die Abarbeitungsreihenfolge in Control FPWIN Pro7.

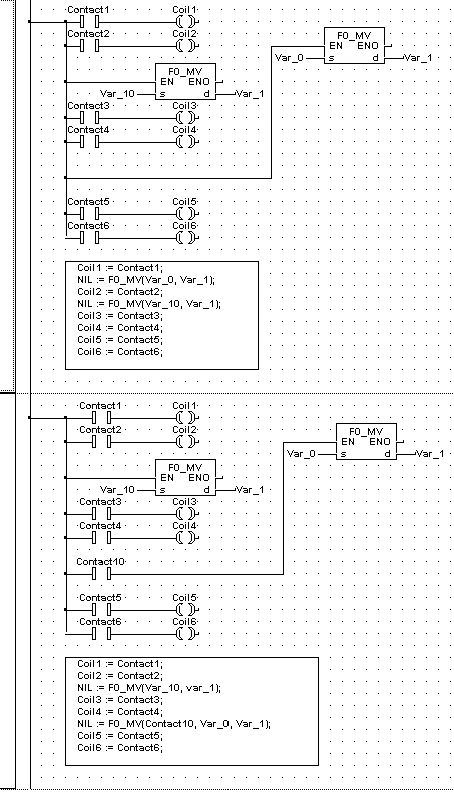

Beispiel 1:

Beispiel 2:

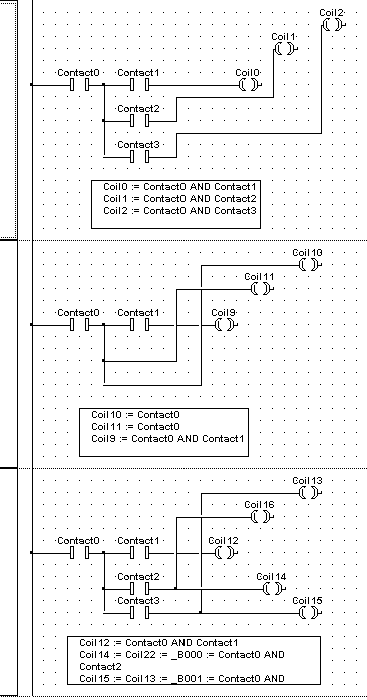

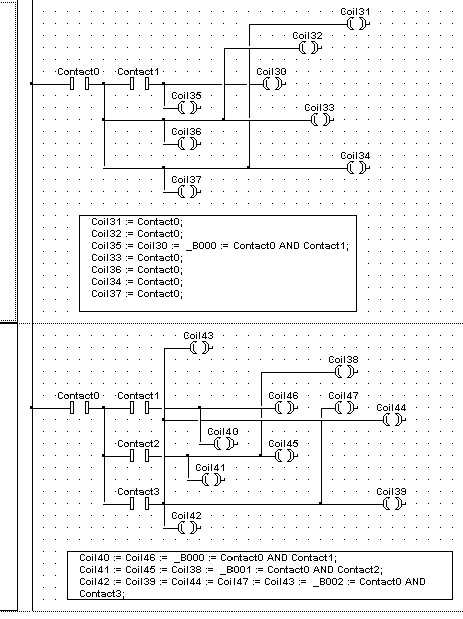

Beispiel 3:

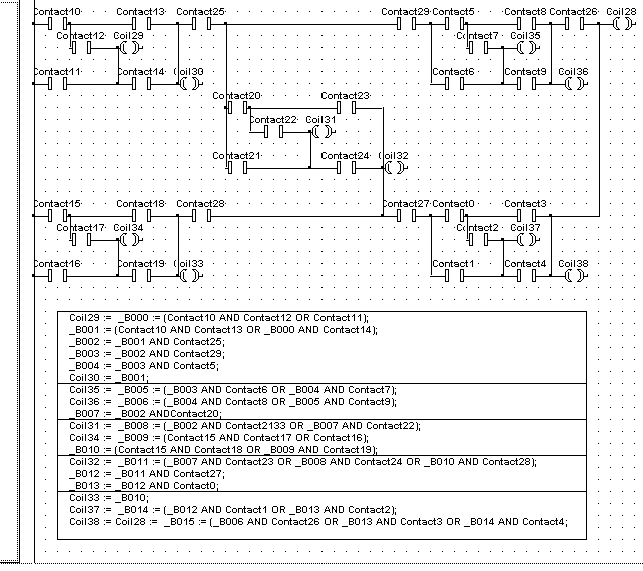

Beispiel 4: